# SPACE VECTOR MODULATION AND CONTROL OF MULTILEVEL CONVERTERS

#### (ABSTRACT)

This dissertation is the result of the research and development of a power conditioning system for superconductive magnetic energy storage systems (SMES). The dominant challenge of this research was to develop a power conditioning system that can match slowly varying dc voltages and dc currents on the superconductive magnet side with the ac voltages and ac currents on the utility side. At the same time, the power conditioning system was required to provide a bi-directional power flow to the superconductive magnet.

The focus of this dissertation is a three-level diode-clamped dc/ac converter, which is a principle part of the power conditioning system. Accordingly, this dissertation deals with the space vector modulation (SVM) of three-level converters and introduces a computationally very efficient three-level SVM algorithm that is experimentally verified.

Furthermore, the proposed SVM algorithm is successfully generalized to allow equally efficient, real-time implementation of SVM to dc/ac converters with virtually any number of levels. The most important advantage of the proposed concept is that the number of instructions required to implement the algorithm is almost independent from the number of levels in a multilevel converter.

More on the side of the control of multilevel converters, particular attention in this dissertation is paid to the problem of charge balance in the split dc-link capacitors of three-level neutral-point-clamped converters. It is a known fact that although the charge balance in the neutral point (NP) can be maintained on a line cycle level, a significant third harmonic current

flows into the NP for certain loading conditions, causing the neutral-point voltage ripple. The logical consequence of that ripple is the deteriorated quality of the output voltage waveforms as well as the increased voltage stress on the switching devices.

This was the motivation to more carefully explore the loading conditions that cause the imbalance, as well as to study the fundamental limitations of dc-link capacitor charge balancing algorithms. As part of this work, a new model of the neutral-point current in the rotating coordinate frame is developed as a tool for the investigation of theoretical limitations and in order to provide some insight into the problem. Additionally, the low-frequency ripple is quantified and guidelines are offered that can help determine the correct size for the dc-link capacitors.

Because the study of the neutral-point balance identified the loading conditions that (under some possible system constraints) cause an unavoidable neutral-point voltage ripple, a feed-forward type of control method is developed next. The proposed feed-forward algorithm can effectively prevent the neutral-point voltage ripple from creating distortions in the converter output voltage under all loading conditions and without causing additional disturbance in the neutral-point voltage. The feed-forward method is developed for a sine triangle as well as for the SVM type PWM algorithm.

The simulation results that include the full dynamic model of the converter and load system validate the feed-forward approach and prove that the feed-forward algorithm can effectively compensate for the effect of the neutral-point voltage ripple. The simulation results are then experimentally verified.

#### **ACKNOWLEDGMENTS**

I wish to express my sincere gratitude to my advisor, Dr. Dushan Boroyevich, for his guidance, encouragement and support during my graduate studies. His impressive knowledge, technical skills and human qualities have been a source of inspiration and a model for me to follow.

I'm also grateful to my professor, Dr. Fred. C. Lee, for his help and guidance during my graduate studies at Virginia Tech. I'm thankful for the opportunity to be a member of the Virginia Power Electronics Center and to watch it grow into the Center for Power Electronics Systems. It has been a memorable experience, both professionally and personally.

I wish to thank my committee members, Dr. William Baumann, Dr. Jason Lai and Dr. Douglas Nelson, for inspiring classes, encouragement in difficult moments and for serving on my advisory committee. At this point, I wish to specifically emphasize my gratiude for all the help and encouragement I received from Dr. Vlatko Vlatkovic and Dr. Jim Lyons from GE CR&D Schenectady, NY. Their guidance and insight gave me encouragement to proceed with confidence towards the completion of this work.

I would also like to acknowledge CPES students and staff for providing an enjoyable educational atmosphere. Especially, I would like to thank my brother Ivan Celanovic for endless discussions, Dr. Dong Ho Lee for sharing with me his rich practical experience, Dengming Peng for working with me on the project, and all others who made my work and my stay in CPES more enjoyable.

With much love, I thank my parents Marija and Lazar for their loving care and their unconditional support. This dissertation is their accomplishment as much as it is mine.

Finally, I would like to thank my good old friend, Dr. Vera Vlahovic, for her support, encouragement in times of need, and her insight.

## **Table of Contents**

| 1 INTRODUCTION                                                         | 1   |

|------------------------------------------------------------------------|-----|

| 1.1 Motivation and Objectives                                          | 1   |

| 1.2 Review of Previous Research                                        | 3   |

| 1.3 Dissertation Outline and Major Results                             |     |

| 2 MULTILEVEL CONVERTERS' MODULATION AND CONTROL                        | 11  |

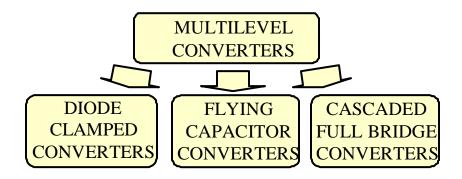

| 2.1 Multilevel Topologies                                              |     |

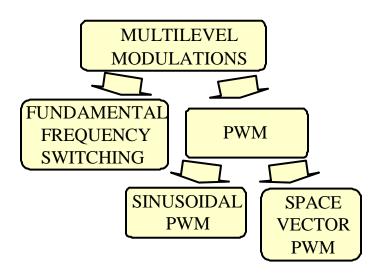

| 2.1.1 Diode-Clamped Multilevel Topology                                |     |

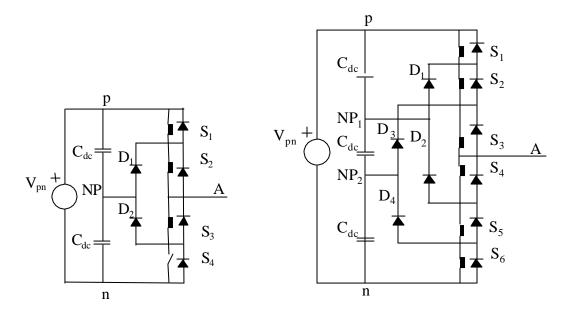

| 2.1.2 Flying Capacitor Multilevel Topology                             |     |

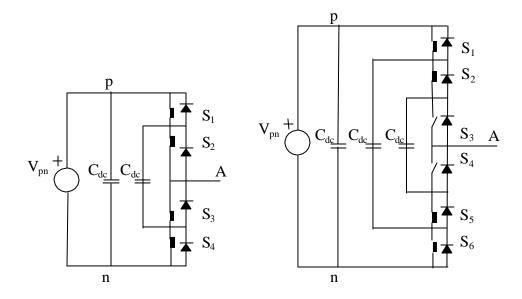

| 2.1.3 Multilevel Configurations with Cascaded Two-Level Full-Bridge In |     |

| 2.1.4 Additional Full-Bridge Topologies                                |     |

| 2.2 Multilevel Digital Control Hardware                                |     |

| 2.2.1 Overview of the Architecture of Digital Control Hardware         |     |

| 2.2.2 Components of the Digital Controller for SMES Power Conditioning |     |

| 2.2.3 Controller Architecture                                          |     |

| 2.2.4 Control Algorithm                                                |     |

| 2.2.5 Functions of the EPLD                                            | 26  |

| 2.3 Multilevel Power Conditioning System as a Power Controller for a   | 2.0 |

| Superconducting Magnetic Energy Storage System                         | 30  |

| 2.3.1 Power Conditioning System Design approach                        |     |

| 2.3.2 Modeling and Control of the Chopper                              |     |

| 2.3.3 Modeling of a Three-Level Voltage Source Inverter                |     |

| 2.3.4 Control of the Inverter in Rotating Coordinates                  |     |

| 2.3.5 Simulation and Experimental Results                              |     |

| 2.4 Modeling and Control Approach and Problem Formulation              |     |

| 2.5 Conclusions  A FAST SPACE VECTOR MODULATION ALGORITHM FOR MUL      |     |

|                                                                        |     |

| CONVERTERS                                                             |     |

| 3.2 Space Vector Modulation of a Three-Level Converter                 |     |

| 3.3 The New Space Vector Modulation Algorithm                          |     |

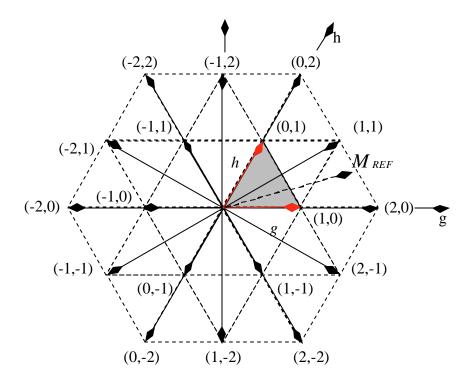

| 3.3.1 Coordinate Transformation                                        |     |

| 3.3.2 Detection of Nearest Three Vectors                               |     |

| 3.3.3 Duty Cycles Computation                                          |     |

| 3.3.4 Switching-State Selection                                        |     |

| 3.4 Practical Implementation of The New SVM Algorithm                  |     |

| 3.5 Conclusions                                                        |     |

| 4 NP BALANCING PROBLEM IN THREE-LEVEL DIODE-CLAMPED                    |     |

| CONVERTERS                                                             |     |

| 4.1 The Effect of Different Switching States on the Current in the NP  |     |

| 4.2 Neutral Point Current Modulation                                   |     |

| 4.3 Analysis and Control of the Neutral Point Voltage Error            | 84  |

| 4.4 Limitations of the Neutral-Point Control and Some Design Recomm    |     |

| 4.5 Experimental Results                                               |     |

|                                                                        |     |

| 4.6   | Conclusions                                                               | 99      |

|-------|---------------------------------------------------------------------------|---------|

| 5     | FEED-FORWARD CONTROL OF THREE-LEVEL NEUTRAL-POINT O                       | CLAMPED |

|       | CONVERTERS                                                                |         |

| 5.1   | The Effect of the Capacitor Charge Imbalance on the Voltage Space Voltage |         |

| 5.2   | Sine Triangle Modulation for Three-Level Converters                       |         |

| 5     | .2.1 PWM Generation with Sine Triangle Modulation                         |         |

| _     | .2.2 NP Control With Sine Triangle Modulation                             |         |

|       | .2.3 The Average Model of a Sine Triangle Modulator                       |         |

|       | Modeling the Feed-Forward Control                                         |         |

|       | .3.1 The Feed-Forward Algorithm                                           |         |

|       | .3.2 Mathematical Basis of the Feed-Forward Algorithm                     |         |

|       | .3.3 Average Model of the Zero-Sequence NP Control                        |         |

|       | .3.4 A Small-Signal Model of the Zero-Sequence NP Control                 |         |

|       | .3.5 The Stability Analysis of the Feed Forward Algorithm                 |         |

| 5.4   | Implementation of Feed-Forward Algorithm for Space Vector Modulation      |         |

| 5.5   | Conclusions                                                               |         |

| 6     | FEED-FORWARD CONTROL OF THREE-LEVEL NEUTRAL-POINT-C                       |         |

|       | CONVERTERS—SIMULATION AND EXPERIMENTAL RESULTS                            |         |

| 6.1   | Analysis and Experimental Verification of the Line Cycle Average Mode     |         |

| Fee   | d-Forward Algorithm                                                       | 129     |

|       | .1.1 Control Authority Over the NP Current, with and without Feed-Forward |         |

|       | Analysis of the Switching-Cycle Average Model of the Sine Triangle Mo     |         |

|       | the Feed-Forward Algorithm                                                |         |

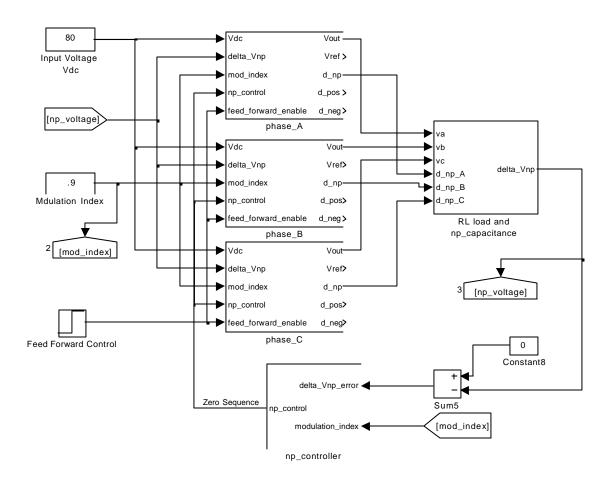

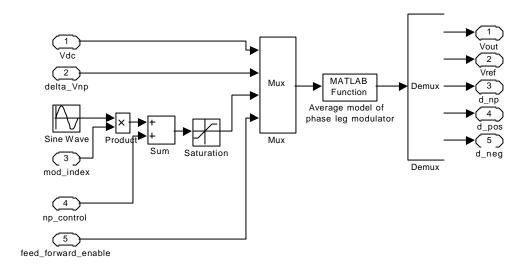

|       | .2.1 Average Model of Three-Level Converter with Sine Triangle Modulator. |         |

|       | .2.2 Performance of Feed-Forward Algorithm, Simulation Results            |         |

|       | Average Model of Fast Space Vector Modulator, Experimental Verificat      |         |

|       | lel                                                                       |         |

|       | .3.1 Average Model of the Three-Level Converter with Fast Space Vector Mo |         |

|       | Algorithm                                                                 |         |

| _     | .3.2 The Fast Space Vector Modulation Algorithm, Experimental Results     |         |

| 6.4   | Conclusions                                                               |         |

| 7     | CONCLUSIONS                                                               |         |

| REFE  | ERENCES                                                                   | 152     |

| VITA. |                                                                           | 159     |

# List of Figures

| Figure 2.1. Multilevel converter topologies.                                                    | 12   |

|-------------------------------------------------------------------------------------------------|------|

| Figure 2.2. Multilevel modulation techniques.                                                   | 12   |

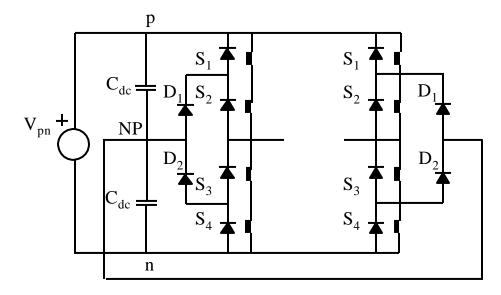

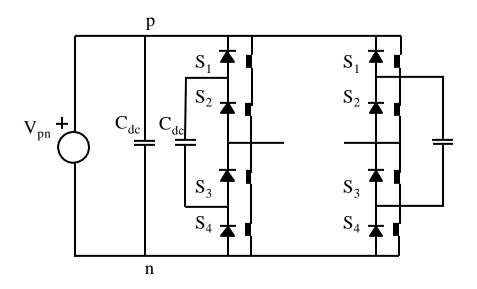

| Figure 2.3. The three- and four-level neutral-point-clamped phase leg.                          | 13   |

| Figure 2.4. Three- and four-level flying capacitor phase leg.                                   | 15   |

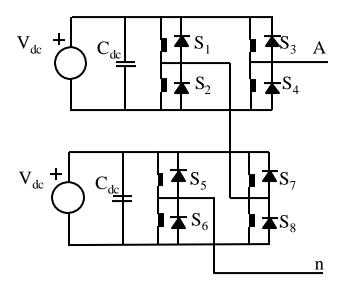

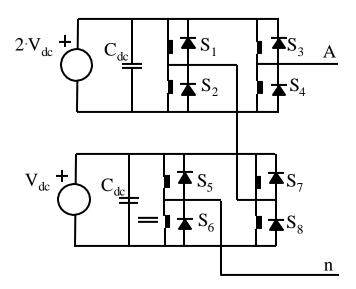

| Figure 2.5. Phase leg of a cascaded five-level full-bridge inverter                             | 16   |

| Figure 2.6. Phase leg of a cascaded full bridge seven-level converter                           | 17   |

| Figure 2.7. Diode clamped full bridge five-level topology                                       | 18   |

| Figure 2.8. Flying capacitor full-bridge five-level topology                                    |      |

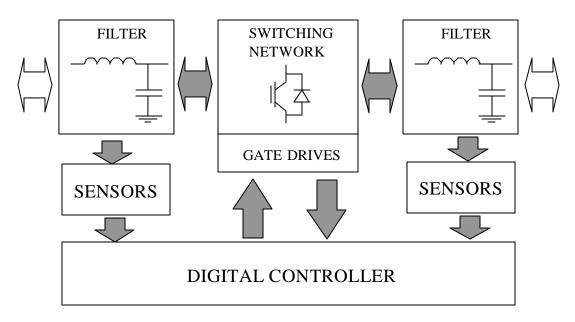

| Figure 2.9. Power electronics system overview.                                                  | 20   |

| Figure 2.10. Architecture of the digital controller for power electronics systems               | . 20 |

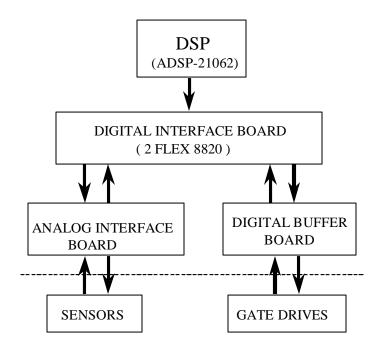

| Figure 2.11. Architecture of the SMES digital controller board                                  | 23   |

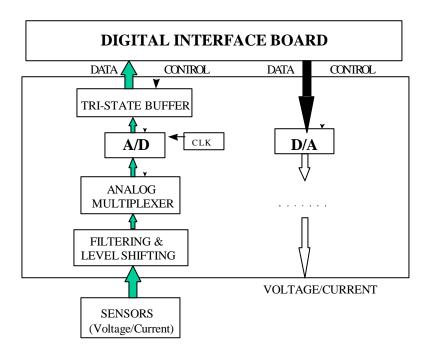

| Figure 2.12. Digital interface board.                                                           | 24   |

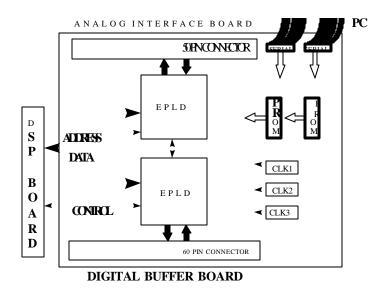

| Figure 2.13. Analog interface board                                                             |      |

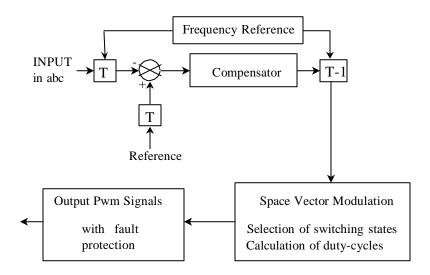

| Figure 2.14. Control overview.                                                                  | 26   |

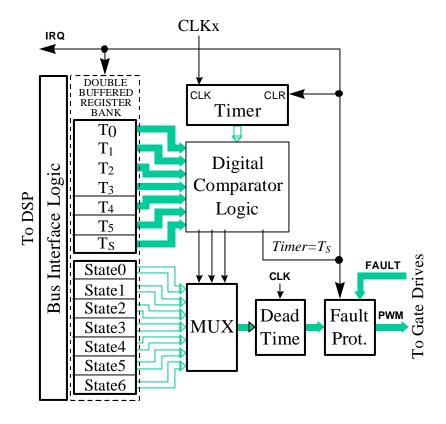

| Figure 2.15. PWM signal generation logic within the EPLD.                                       | 27   |

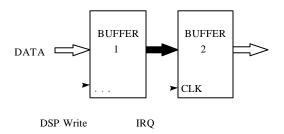

| Figure 2.16. A double-buffered register bank inside the EPLD                                    | 27   |

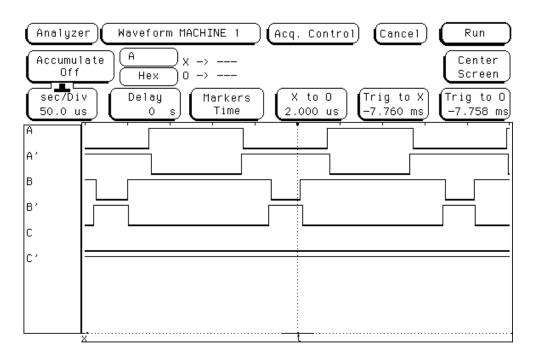

| Figure 2.17. Inverted gate drive signals with dead-time.                                        | 29   |

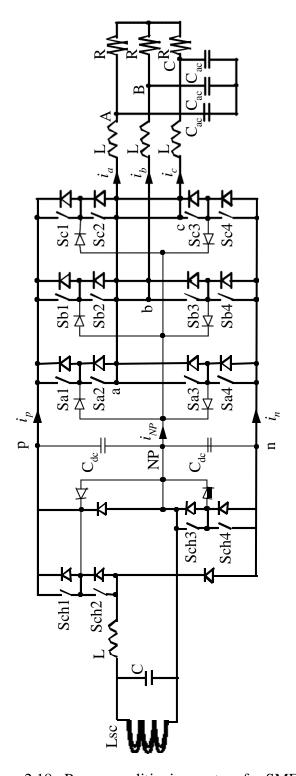

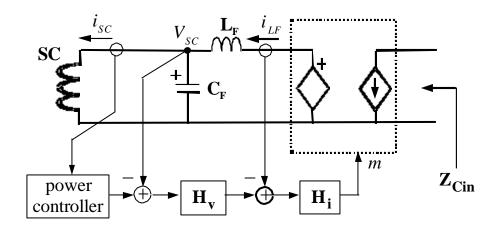

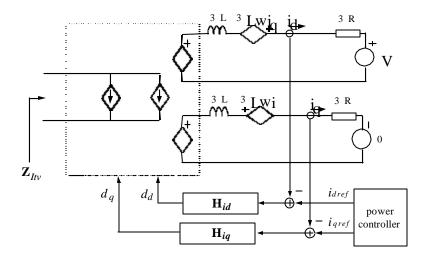

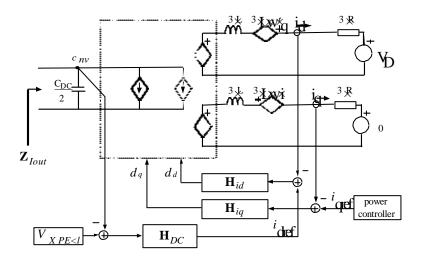

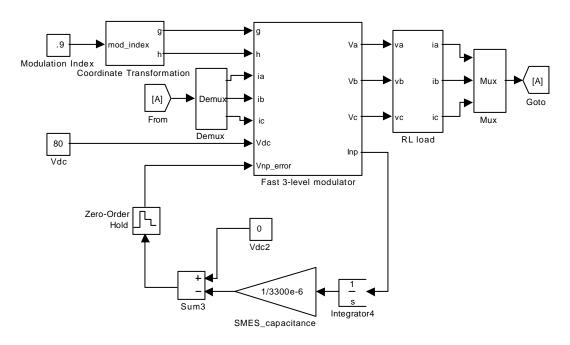

| Figure 2.18. Power conditioning system for SMES                                                 | 32   |

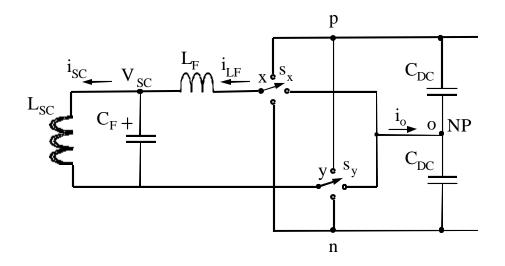

| Figure 2.19. Equivalent switching model of three-level chopper                                  | 34   |

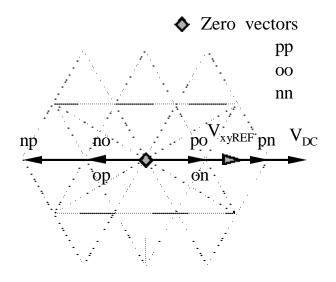

| Fig. 2.20. Space voltage vectors of the chopper                                                 | 34   |

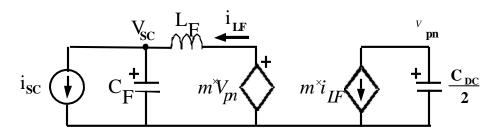

| Figure 2.21. Average model of the chopper                                                       |      |

| Figure 2.22. Buck mode control of the chopper (charging the SC).                                | 37   |

| Figure 2.23. Boost mode control of the chopper (discharging the SC)                             | 37   |

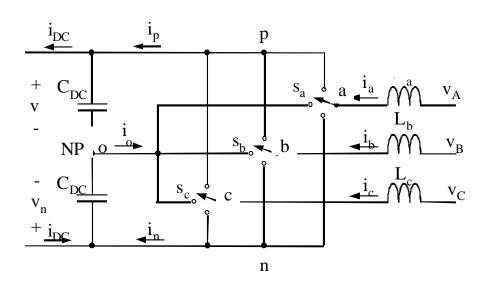

| Figure 2.24. Switching network of a three-level VSI                                             |      |

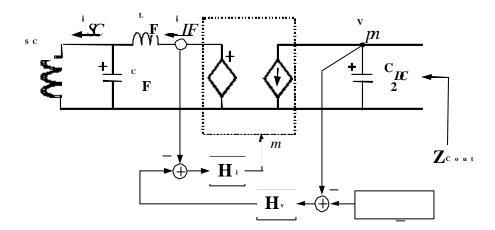

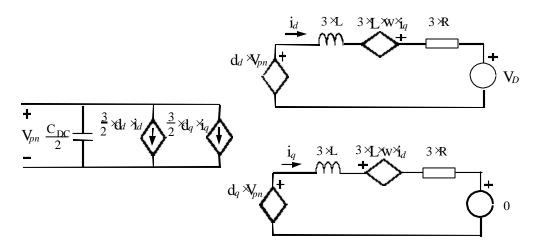

| Figure 2.25. Inverter average model in rotating d-q coordinate frame.                           | 42   |

| Figure 2.26. Inverter control in the utility mode (charging the SC).                            |      |

| Figure 2.27. Inverter control in rectifier mode (discharging the SC)                            |      |

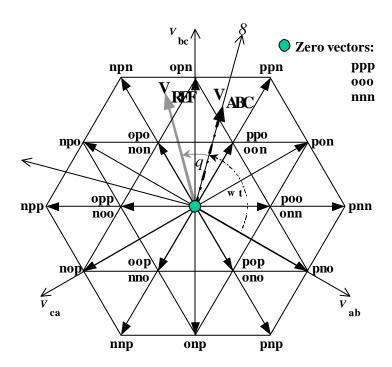

| Figure 2.28. Voltage space vectors of a three-level inverter                                    |      |

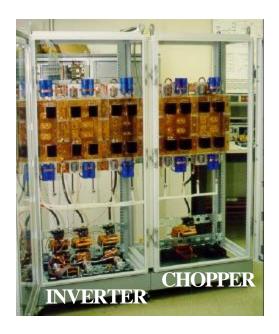

| Figure 2.29. Experimental SMES PCS system.                                                      |      |

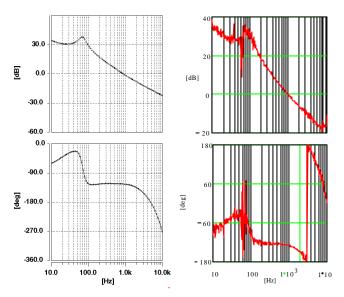

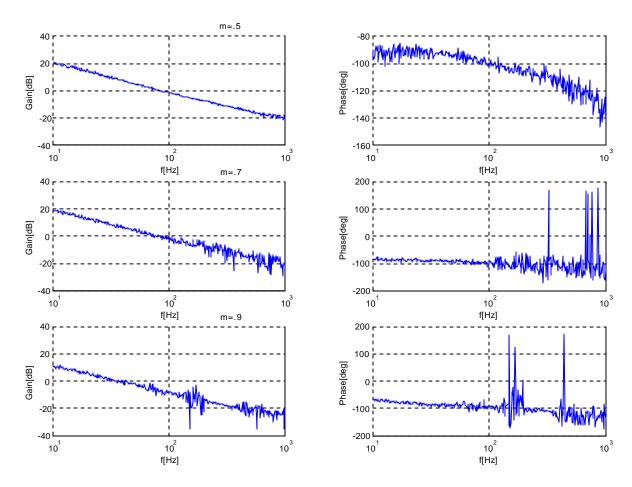

| Figure 2.30. Simulated and measured rectifier current loop gain.                                | 47   |

| Figure 2.31. Simulated and measured rectifier voltage loopgain                                  | 47   |

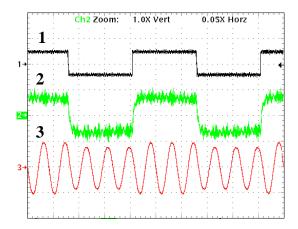

| Figure 2.32. Rectifier response to change in current command                                    |      |

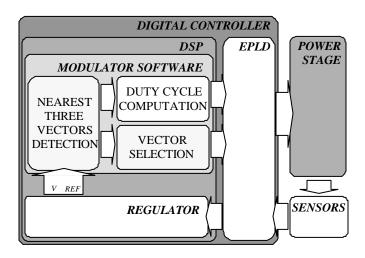

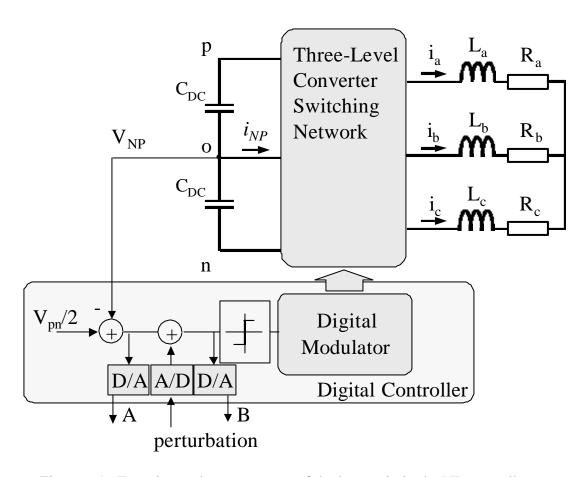

| Figure 3.1. Architecture of digital controller for three-phase converters                       | 51   |

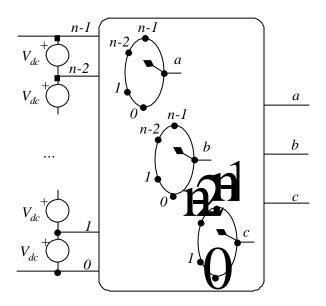

| Figure 3.2. Functional diagram of a three-leg n-level converter                                 |      |

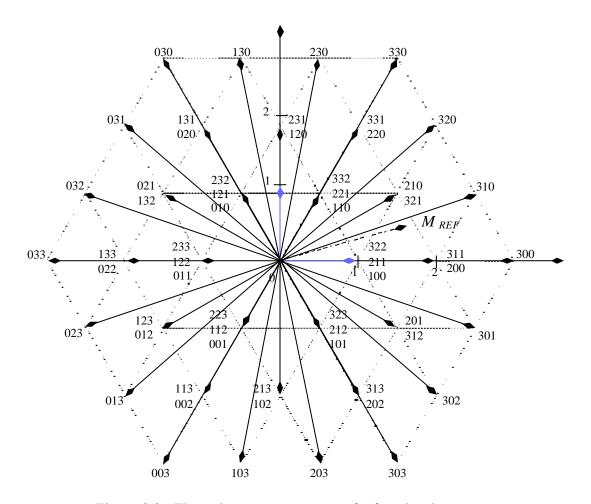

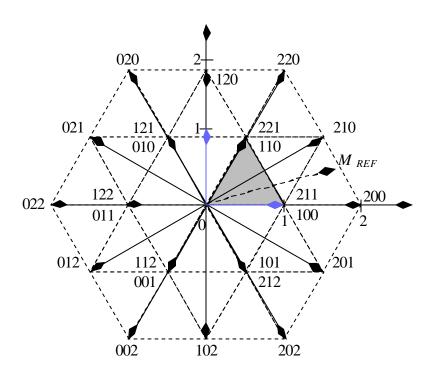

| Figure 3.3. Switching states of a three-level converter                                         |      |

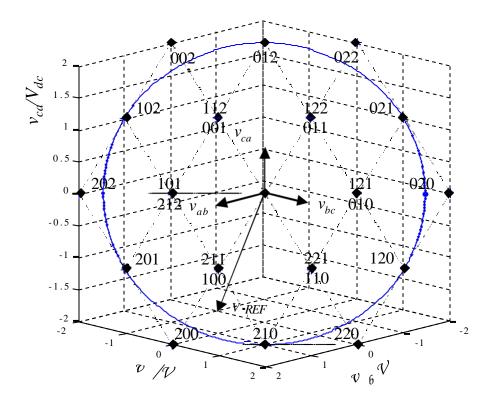

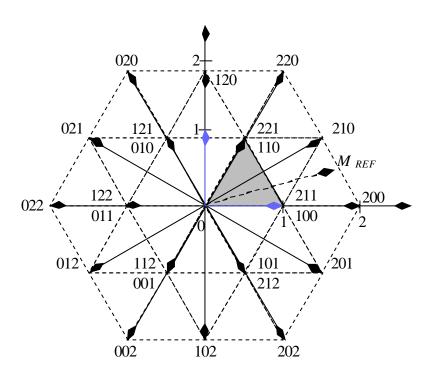

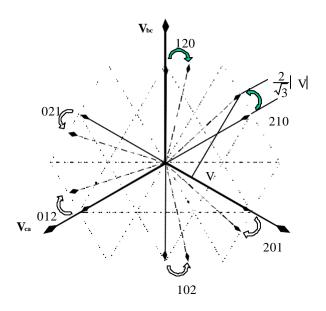

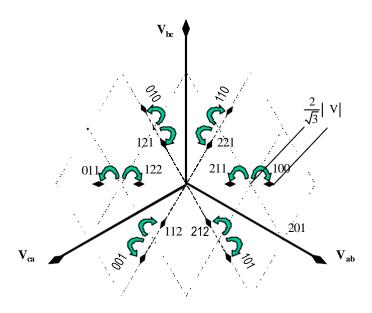

| Figure 3.4. Voltage space vectors of a three-level converter                                    |      |

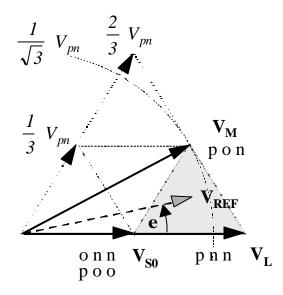

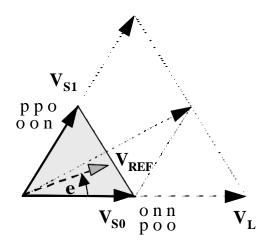

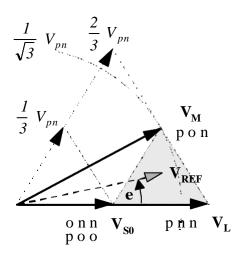

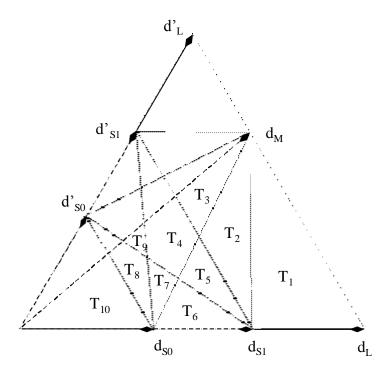

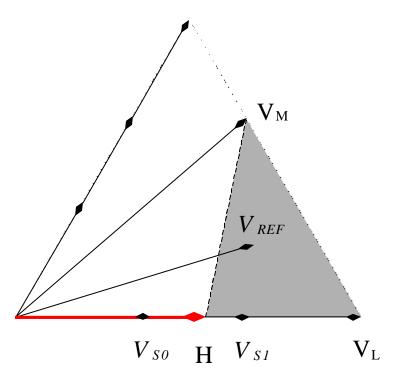

| Figure 3.5. Synthesis of $V_{REF}$ in outer small triangle.                                     | 59   |

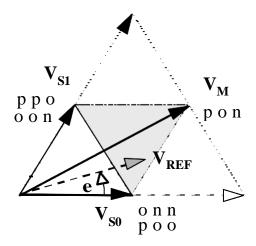

| Figure 3.6. Synthesis of $V_{REF}$ in middle small triangle                                     | 60   |

| Fig. 3.7. Synthesis of $V_{REF}$ in inner small triangle.                                       |      |

| Figure 3.8. The voltage space vectors of a four-level converter                                 |      |

| Figure 3.9. Switching-state vectors of a three-level converter in a hexagonal coordinate system | a.   |

|                                                                                                 | 64   |

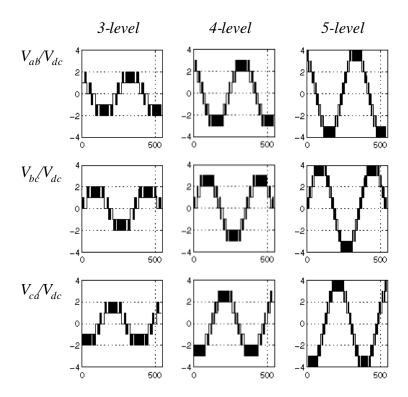

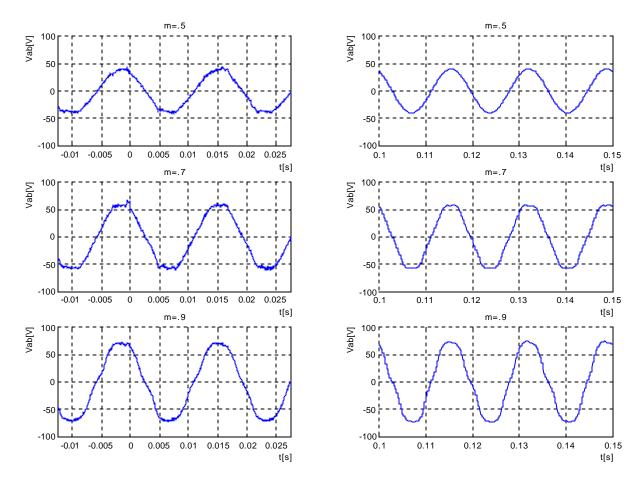

| Figure 3.10. Normalized line-to-line PWM voltage waveforms for three-, four- and five-level for three-, four- and five- and | vel |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68  |

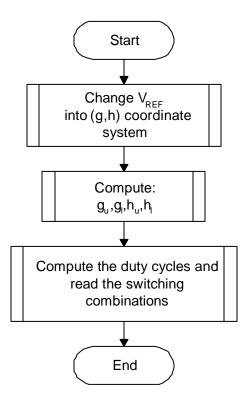

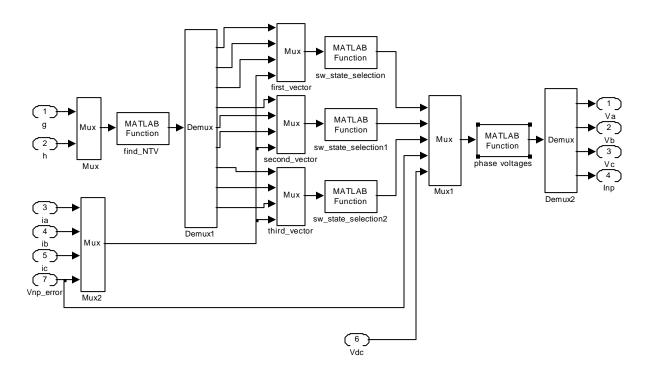

| Figure 3.11. Overview of the new SVM algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 69  |

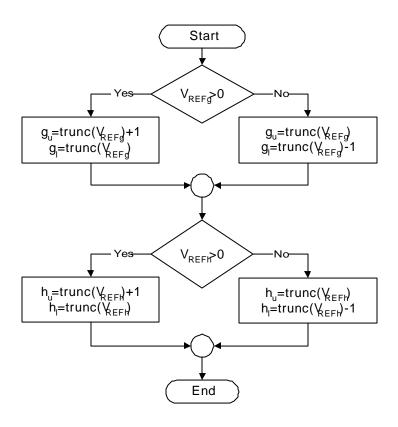

| Figure 3.12. Computing the nearest four vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

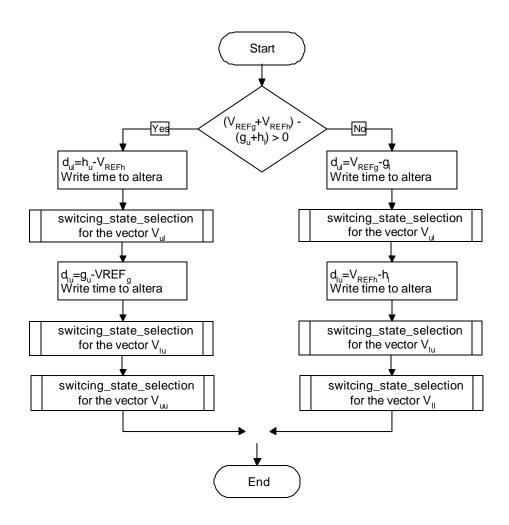

| Figure 3.13. Computation of duty cycles and selection of switching states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71  |

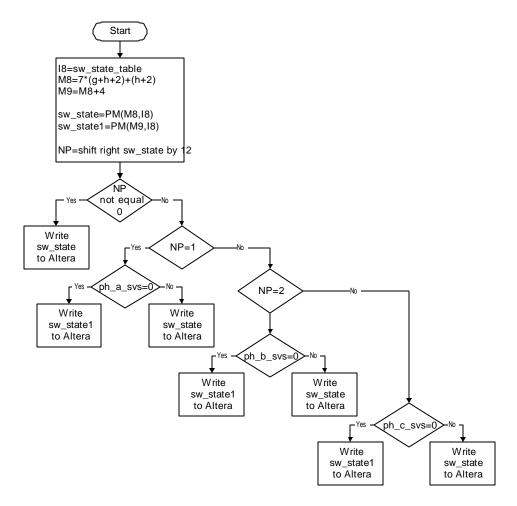

| Figure 3.14. Switching-state selection with dc-link capacitor charge control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

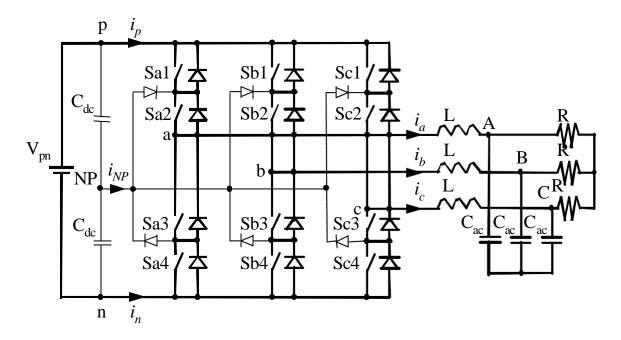

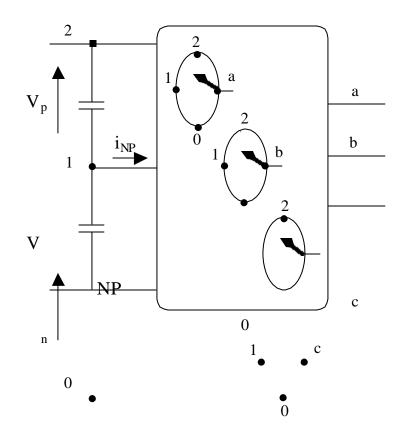

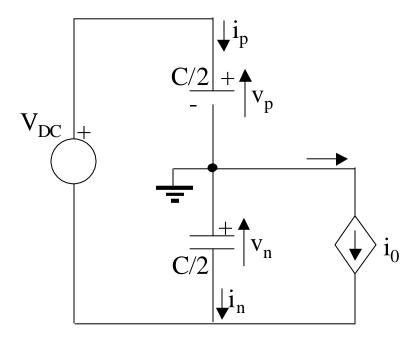

| Figure 4.1. Circuit schematic of a three-level VSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

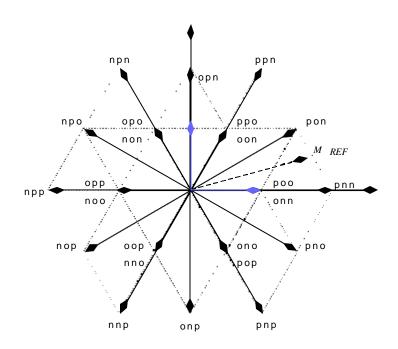

| Figure 4.2. Switching-state vectors of the three-level VSI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

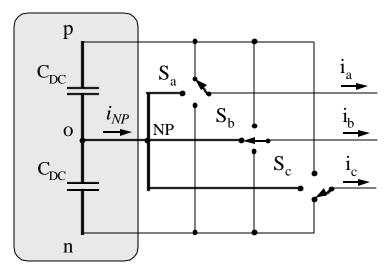

| Figure 4.3. The position of equivalent switches for the switching state <b>pon</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

| Figure 4.4. Outer small triangle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

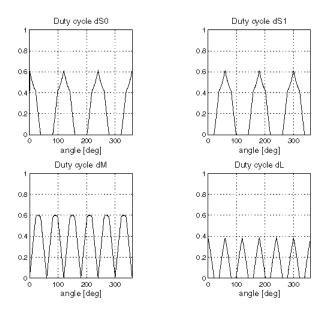

| Figure 4.5. Duty cycles of SVM for modulation index m=0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

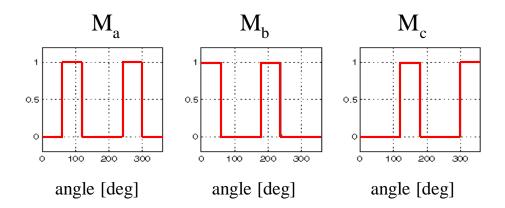

| Figure 4.6. Switching functions of the medium vectors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 86  |

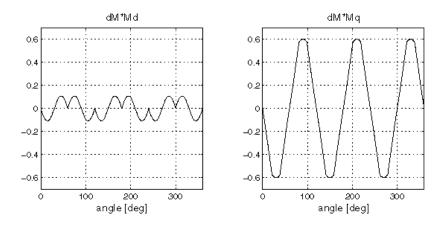

| Figure 4.7. Weighing factors for medium vectors with m=0.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 90  |

| Figure 4.8. Weighing factors for small vectors with m=0.8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

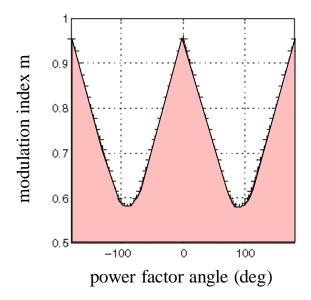

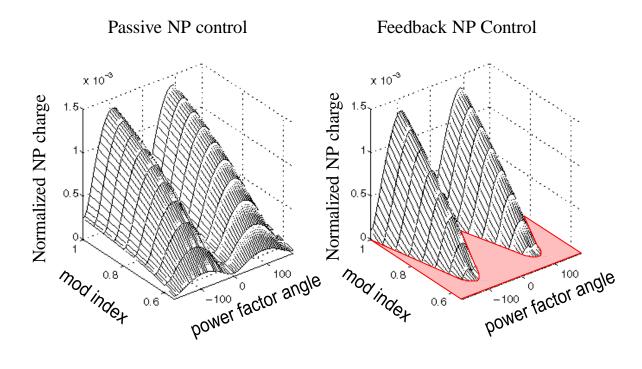

| Figure 4.9. Region where LF ripple can be suppressed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

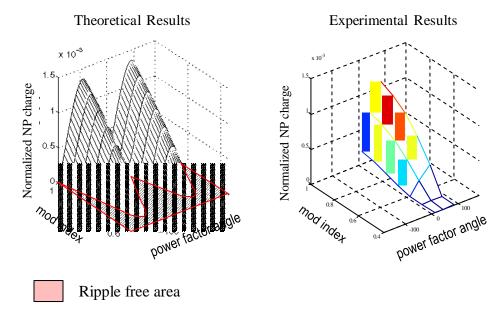

| Figure 4.10. Normalized amplitude of the LF charge ripple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

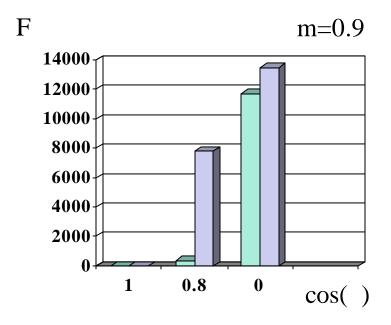

| Figure 4.11. Capacitor sizes for specified NP ripple, with and without NP control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

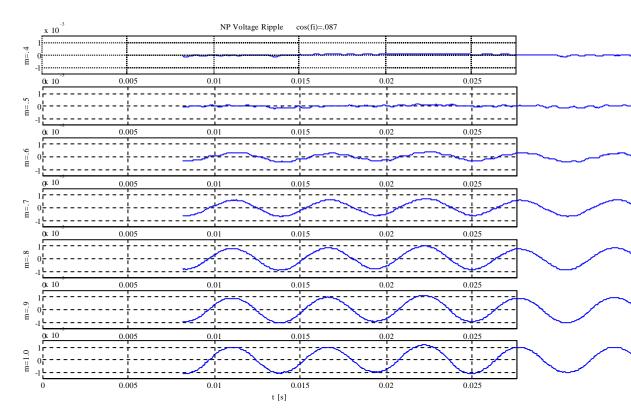

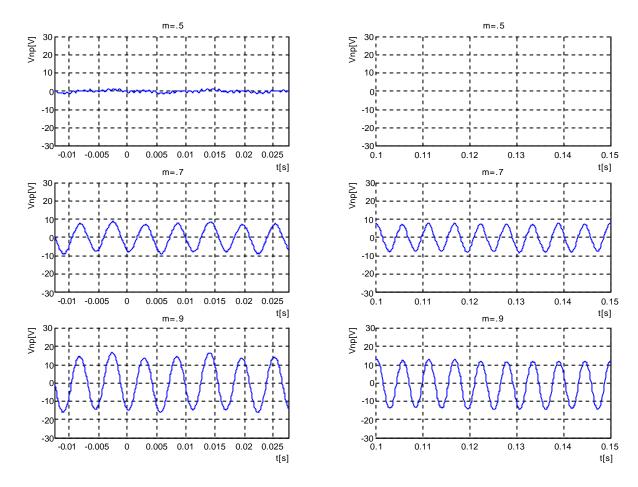

| Figure 4.12. Experimental verification of NP voltage ripple properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| Figure 4.13. Normalized NP voltage for power factor angle of 85 degrees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| Figure 4.14. Theoretical and experimental normalized NP voltage ripple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

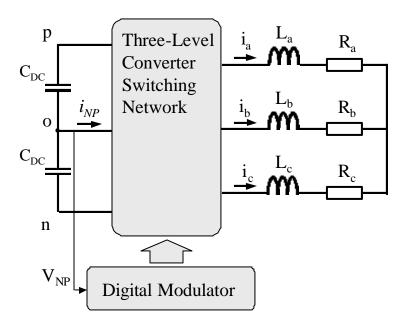

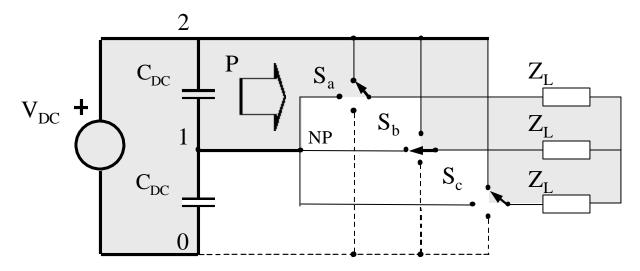

| Figure 5.1. Functional diagram of a three-level converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| Figure 5.2. Voltage space vectors of a three-level converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

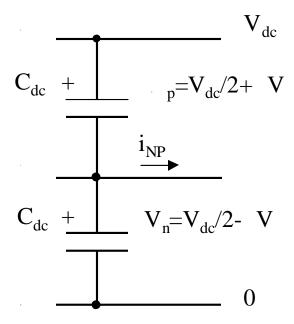

| Figure 5.3. The definitions of the dc-link voltages and the voltage error in the NP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| Figure 5.4. Shift of the medium voltage vectors due to the V>0 error in NP voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 104 |

| Figure 5.5. "Splitting" of the small voltage vectors due to the V>0 error in NP voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 105 |

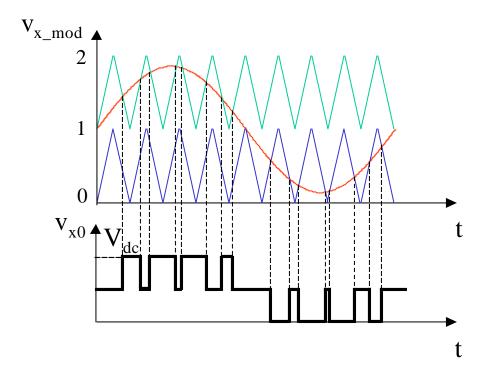

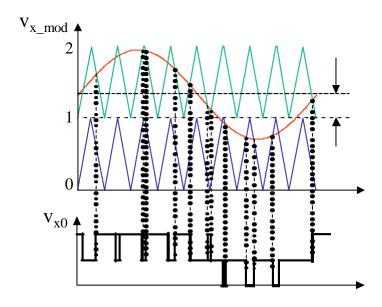

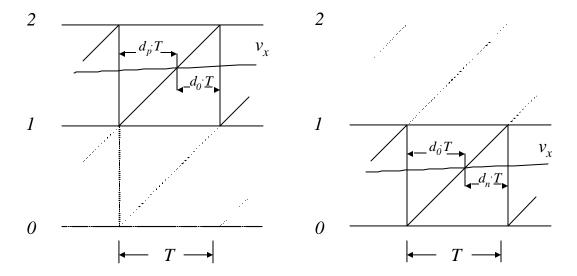

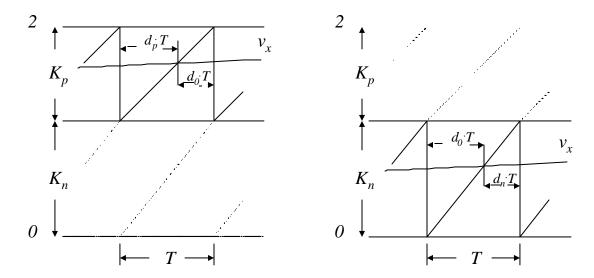

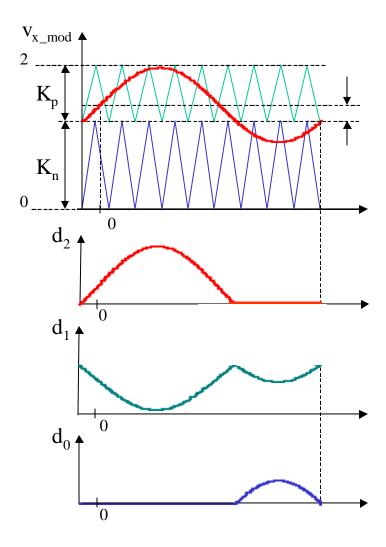

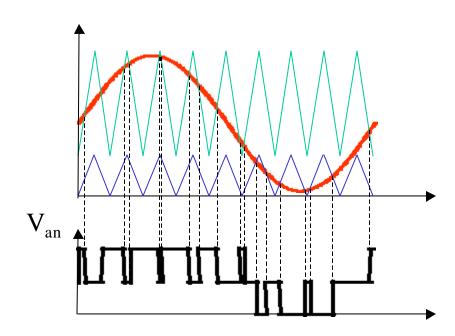

| Figure 5.6. Principle of sine triangle modulation for a three-level converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| Figure 5.7. Principle of NP control for the three-level converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

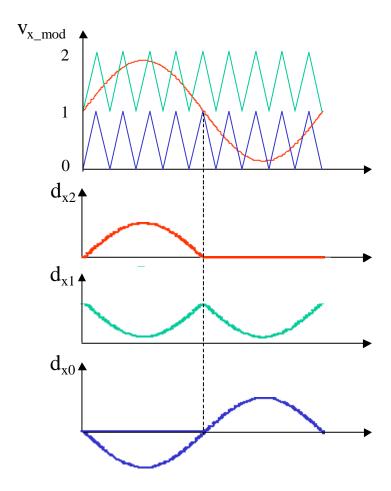

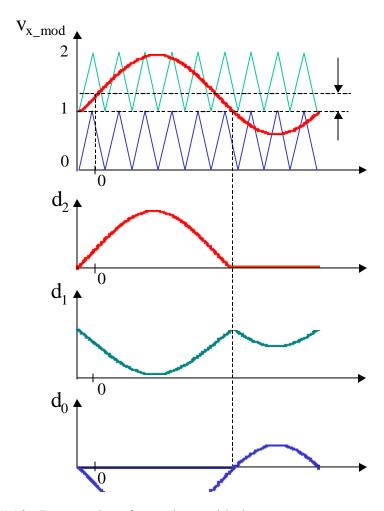

| Figure 5.8. Duty cycles for the sine triangle three-level modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| Figure 5.9. Duty cycle of one phase equivalent switch for sine triangle modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

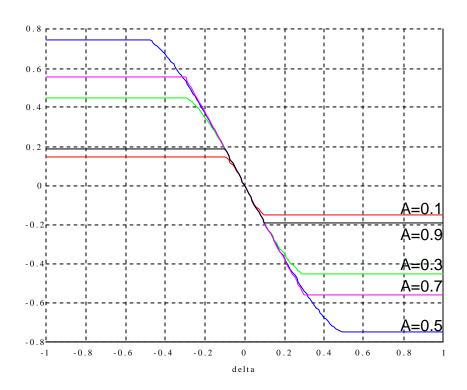

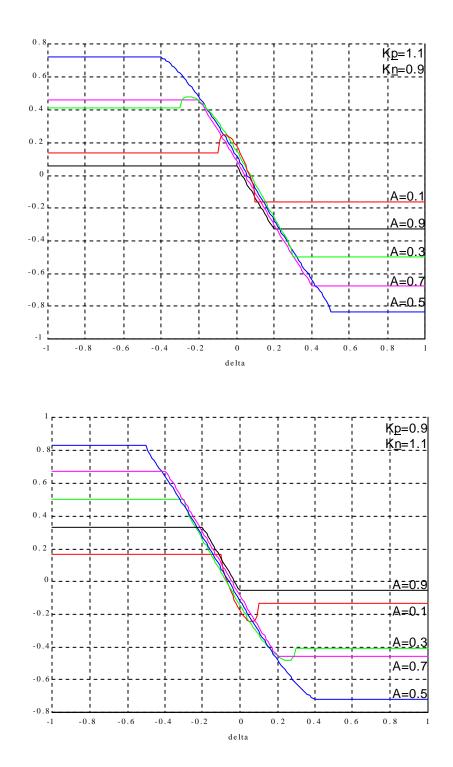

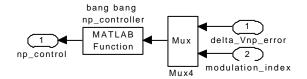

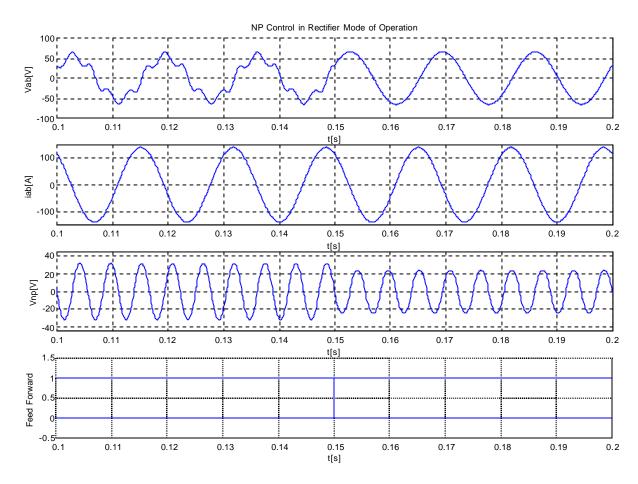

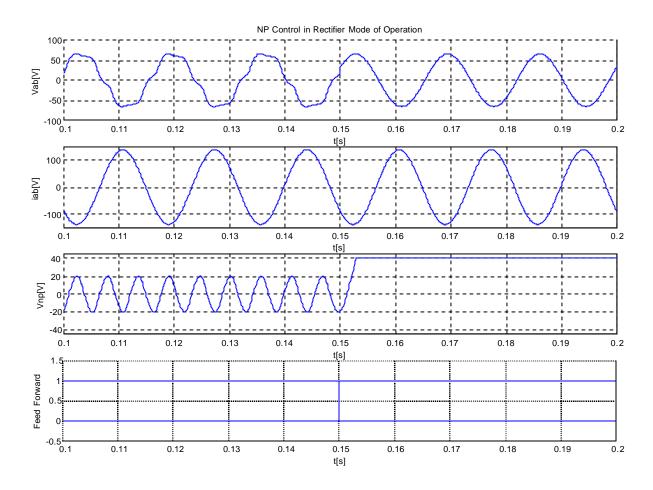

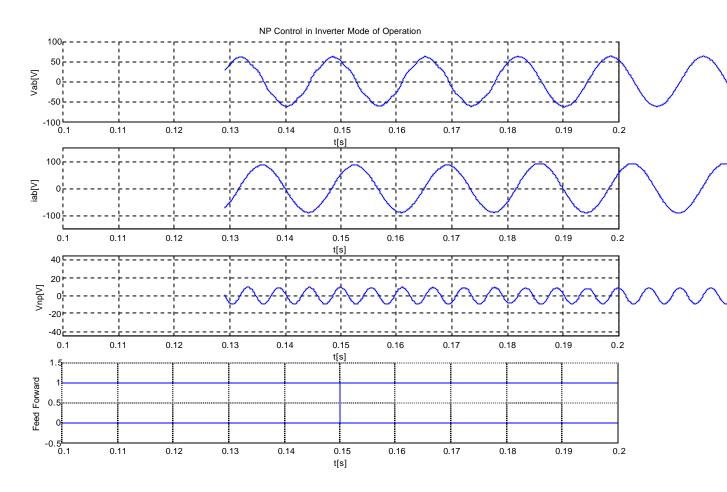

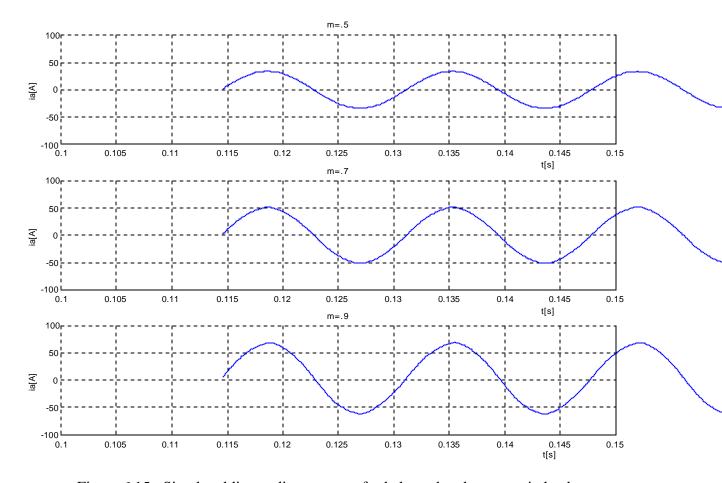

| Figure 5.10. Duty cycles of one phase with the zero sequence present                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |